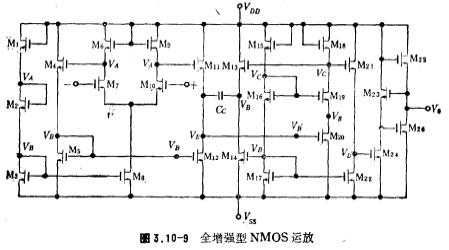

NMOS运放典型电路图1、全增强型NMOS运放全增强型NMOS运放如图3.10-9所示。构成输入级差分电路,其增益约5倍;image.png和image.png为电平位移电路,增益约0.95倍;image.png组成串级放大和输出级驱动电路,采用串级放大是为了减少M20栅极的密勒电容,以改善频率响应,这一级的增益等于image.png,约为11倍;image.png构成输出级电路,其形式如图3.1

NMOS运放典型电路图1、全增强型NMOS运放全增强型NMOS运放如图3.10-9所示。构成输入级差分电路,其增益约5倍;image.png和image.png为电平位移电路,增益约0.95倍;image.png组成串级放大和输出级驱动电路,采用串级放大是为了减少M20栅极的密勒电容,以改善频率响应,这一级的增益等于image.png,约为11倍;image.png构成输出级电路,其形式如图3.1

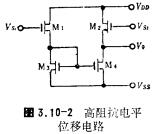

NMOS单级放大器电平位移电路,从电路性能来说,单沟NMOS运放比CMOS运放差,因为它缺少互补器件,电路形式也较复杂。但是,由于NMOS电路的速度与集成度均比CMOS电路水平高,因此,在LSIMOS模拟集成电路中,它是很有吸引力的。特别是当MOS模拟电路中包含了电荷转换器件时,通常采用NMOS工艺来实现。实际上,首次出现的全MOS运放电路就是NMOS到的运放。NMOS运放与CMOS运放相比,它

NMOS单级放大器电平位移电路,从电路性能来说,单沟NMOS运放比CMOS运放差,因为它缺少互补器件,电路形式也较复杂。但是,由于NMOS电路的速度与集成度均比CMOS电路水平高,因此,在LSIMOS模拟集成电路中,它是很有吸引力的。特别是当MOS模拟电路中包含了电荷转换器件时,通常采用NMOS工艺来实现。实际上,首次出现的全MOS运放电路就是NMOS到的运放。NMOS运放与CMOS运放相比,它

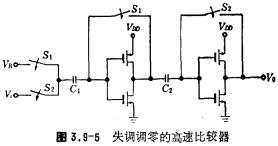

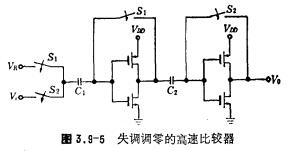

CMOS电压比较器工作原理,为提高电压比较器的灵敏度,可采用上一节介绍的失调自动调零技术,其电路形式如图3.9-3所示,该电路同本章第八节图3.8-5电路相似,其失调自动调零原理已作了说明,图3.9-3的电路是低失调电压比较器电路。下面简要介绍该电压比较器的工作原理。图中VR为基准电压,Vi>VR为输入信号电压。电路的工作状态可由双相时钟信号控制。第一种工作状态,当开关S1闭合,而S2断开的时候,

CMOS电压比较器工作原理,为提高电压比较器的灵敏度,可采用上一节介绍的失调自动调零技术,其电路形式如图3.9-3所示,该电路同本章第八节图3.8-5电路相似,其失调自动调零原理已作了说明,图3.9-3的电路是低失调电压比较器电路。下面简要介绍该电压比较器的工作原理。图中VR为基准电压,Vi>VR为输入信号电压。电路的工作状态可由双相时钟信号控制。第一种工作状态,当开关S1闭合,而S2断开的时候,

CMOS电压比较器工作原理及特点,电压比较器在电路结构、电性能等方面与运放基本相同,而其符号表示也与运放完全一致,即有同相和反相二个输入端,一个输出端,开环增益用A表示。电压比较器的功能是比较两个模拟输入信号的大小,并在输出端得到高电平或低电平。若用V+,和V-分别表示同相输入端和反相输入端电压,那么对于理想的电压比较器,其特性可表示为:当V+大于V-时,它的输出是高电平;当V-大于V+时,它的输

CMOS电压比较器工作原理及特点,电压比较器在电路结构、电性能等方面与运放基本相同,而其符号表示也与运放完全一致,即有同相和反相二个输入端,一个输出端,开环增益用A表示。电压比较器的功能是比较两个模拟输入信号的大小,并在输出端得到高电平或低电平。若用V+,和V-分别表示同相输入端和反相输入端电压,那么对于理想的电压比较器,其特性可表示为:当V+大于V-时,它的输出是高电平;当V-大于V+时,它的输

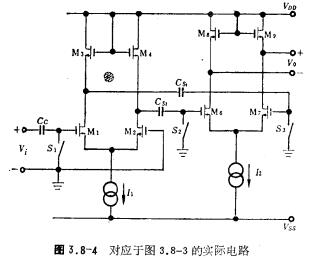

MOS运放的自动调零,在MOS模拟大规模集成电路中,作为主要部件的MOS运放,其电路结构越简单越好,以减小芯片的面积;但一般的MOS运放其失调电压都较大,约10~20毫伏,这样限制了它的使用范围。为了减低一般结构的MOS运放失调和漂移,我们可采用便于集成的自动调零技术,具体阐述如下。图3.8-3电路是失调电压自动调零的MOS放大器电路原理图。

MOS运放的自动调零,在MOS模拟大规模集成电路中,作为主要部件的MOS运放,其电路结构越简单越好,以减小芯片的面积;但一般的MOS运放其失调电压都较大,约10~20毫伏,这样限制了它的使用范围。为了减低一般结构的MOS运放失调和漂移,我们可采用便于集成的自动调零技术,具体阐述如下。图3.8-3电路是失调电压自动调零的MOS放大器电路原理图。

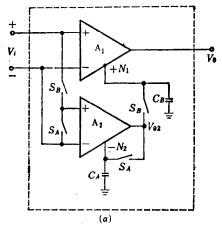

ICL7650的工作原理图,MOS技术设计的动态较零CMOS运放ICL7650,其失调为0.01微伏,温度漂移为0.01微伏/℃,开环增益达130分贝,共模抑制比为130分贝。可以这样说,动态校零的CMOS运放ICL7650,在直流特性方面已经接近于“理想”运放,从而使集成运放进入了第四代,并确立了MOS运放在模拟集成电路中的重要地位。本节将介绍动态校零CMOS集成运放ICL7650的设计思想,并

ICL7650的工作原理图,MOS技术设计的动态较零CMOS运放ICL7650,其失调为0.01微伏,温度漂移为0.01微伏/℃,开环增益达130分贝,共模抑制比为130分贝。可以这样说,动态校零的CMOS运放ICL7650,在直流特性方面已经接近于“理想”运放,从而使集成运放进入了第四代,并确立了MOS运放在模拟集成电路中的重要地位。本节将介绍动态校零CMOS集成运放ICL7650的设计思想,并

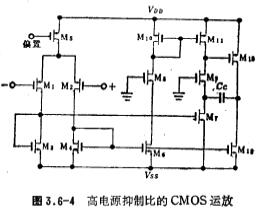

高性能CMOS功率运放,图中的前置放大器(M1~M11)与前一节图3.6-4高电源抑制比运放的电路结构相同,因此图3.7-8功率运放具有高电源抑制比。图中的输出级部分与图3.7-6电路相同,MH1~MH11构成A1放大器,ML2~ML11构成A2放大器,MH3和M15提供正向输出电流,image.png和M17,吸入负向电流,Cc1、Cc2和Cc3分别为前置放大器、A1放大器和A2放大器的须率补偿

高性能CMOS功率运放,图中的前置放大器(M1~M11)与前一节图3.6-4高电源抑制比运放的电路结构相同,因此图3.7-8功率运放具有高电源抑制比。图中的输出级部分与图3.7-6电路相同,MH1~MH11构成A1放大器,ML2~ML11构成A2放大器,MH3和M15提供正向输出电流,image.png和M17,吸入负向电流,Cc1、Cc2和Cc3分别为前置放大器、A1放大器和A2放大器的须率补偿

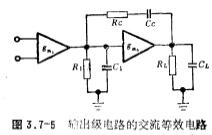

CMOS输出电路,CMOS输出电路原理,图中放大器A1与输出管M1构成全负反馈放大器,其正向输出增益为1;放大器A2与输出M2构成全负反馈放大器,其负向输出增益也为1。在静态条件下,M1和M2均处于截止状态,这时输出电路由M5和M6来承担,其静态电流由M2、M4偏置电路来提供。为了保证在静态条件下,M1和M2截止,因此在设计A1和A2放大时,人为地引入失调电压Vos(使A1和A2放大器的输入差分对

CMOS输出电路,CMOS输出电路原理,图中放大器A1与输出管M1构成全负反馈放大器,其正向输出增益为1;放大器A2与输出M2构成全负反馈放大器,其负向输出增益也为1。在静态条件下,M1和M2均处于截止状态,这时输出电路由M5和M6来承担,其静态电流由M2、M4偏置电路来提供。为了保证在静态条件下,M1和M2截止,因此在设计A1和A2放大时,人为地引入失调电压Vos(使A1和A2放大器的输入差分对

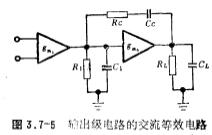

CMOS功率输出级电路,前面介绍的CMOS运放,大都采用共源输出级电路,因而输出阻抗较高,且驱动力也较差。CMOS功率输出级电路。本节将讨论输出阻抗低,能驱动大容负载(包括低阻值的电阻负载)、静态功耗小的CMOS功运放,CMOS功率运放的设计包括两部分,即前置放大和输出级,而前置放大器的设计同前面讨论的各类CMOS运放的设计没有什么区别,因此本节主要讨论CMOS功率运放输出级电路的设计方法。

CMOS功率输出级电路,前面介绍的CMOS运放,大都采用共源输出级电路,因而输出阻抗较高,且驱动力也较差。CMOS功率输出级电路。本节将讨论输出阻抗低,能驱动大容负载(包括低阻值的电阻负载)、静态功耗小的CMOS功运放,CMOS功率运放的设计包括两部分,即前置放大和输出级,而前置放大器的设计同前面讨论的各类CMOS运放的设计没有什么区别,因此本节主要讨论CMOS功率运放输出级电路的设计方法。

CMOS提高电源抑制比,图3.6-1所示的运放电路的电源抑制比之所以比较差,主要是由于电源变化的信号通过补偿电容耦合到输出端所引起的。若对图3.6-1运放电路作些改进,将其输入端改为共源一共栅形式,则其电源抑制比的性能将得到改善,其具体的电路形式如图3.6-2所示。当电源VDD有一变化信号Vs,则在输出管image.png的栅极也有同样变化的信号。引入共栅电路image.png后,其漏极的信号对源

CMOS提高电源抑制比,图3.6-1所示的运放电路的电源抑制比之所以比较差,主要是由于电源变化的信号通过补偿电容耦合到输出端所引起的。若对图3.6-1运放电路作些改进,将其输入端改为共源一共栅形式,则其电源抑制比的性能将得到改善,其具体的电路形式如图3.6-2所示。当电源VDD有一变化信号Vs,则在输出管image.png的栅极也有同样变化的信号。引入共栅电路image.png后,其漏极的信号对源