电子技术论坛

信息来源: 时间:2021-4-22

MOS集成电路设计要点及几何尺寸的确定等详解

(1)对寄生元件的考虑

MOS集成电路的设计与作为分立元件的MOS晶体管的设计不同,集成电路内部的杂散电容小,为了得到一定的速度,gm可以做得很小,可以使晶体管的面积做得很小;同时集成电路的元件之间必需隔离。MOS集成电路设计要点。关于隔离的问题,如图3.19所示,若氧化膜跨过两个扩散层穿接区,在氧化膜上又有金属布线时,相当于在该处构成了一个MOS晶体管,在集成电路中意识不到的部分可能产生晶体管的作用。象这样的由布线等原因出现的MOS晶体管称为寄生MOS晶体管7)。

为了使寄生MOS晶体管在电路的偏压下不工作,通常要增厚金属布线下的氧化层以减小该晶体管的gm,另外,要尽可能将寄生晶体管的阈值电压设计得高于偏压。这相当于双极型集成电路的隔离。如系互补型的场合,一般将N沟道晶体管进行隔离。

(2)材料常数的决定

制造MOS集成电路时,须决定半导体(目前是硅)衬底的杂质浓度NB、栅氧化膜厚度Tox1、栅电极材料、布线下的氧化膜厚度Tox2等材料常数。设计时各种常数值应满足表的条件。表3.7中的μcff除了随衬底杂质浓度变化外,还随栅氧化膜的特性变化。用SiO2作氧化膜时Qo为正号,用氧化铝时则为负号。MOS集成电路设计要点。衬底杂质浓度较高时,容易隔离,但μcff下降8),Vth增大到所要求的值以上,所以浓度值应适当,通常取NB=1015~1016原子/cm3,Tox1=1,000~2,000 ,Tox2=1~1.5μ左右的值。SiO2在含五氧化二磷的气氛中进行高温磷处理,可使器件稳定。栅氧化膜的耐压为100V左右,所以要在与外引线相连的栅上接一个并联的反向偏置P·N结二极管(保护二极管),以防止带电造成的绝缘破坏。

,Tox2=1~1.5μ左右的值。SiO2在含五氧化二磷的气氛中进行高温磷处理,可使器件稳定。栅氧化膜的耐压为100V左右,所以要在与外引线相连的栅上接一个并联的反向偏置P·N结二极管(保护二极管),以防止带电造成的绝缘破坏。

(3)几何尺寸的确定

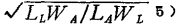

在源接地负载的情形,放大晶体管与负载晶体管的L和W,可以是同一量级的,但在漏接地负载晶体管中,尺寸比决定了增益和输出电压。电压传输特性线性部分的增益G为

,输入电压增加时,在过激励区域

,输入电压增加时,在过激励区域

的输出电压(导通电压)大致为

的输出电压(导通电压)大致为

杂质浓度增加时,电压增益较上述简单公式为小,应予修正。放大晶体管与负载晶体管的尺寸比要选择得能满足修正衬底效应的要求及所要求的增益和电压。MOS集成电路设计要点。LA选择光刻技术精确度所能实现的最小尺寸,WA值是考虑了负载电容等因素后可实现所需的gm(或驱动电流)而加以选取的。WL可选取与LA同一量级。LL由尺寸比和其它三个W、L值决定。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助