电子技术论坛

信息来源: 时间:2022-8-29

解析MOS晶体管版图及其设计绘图示意说明

本节简短讨论一下制造一整套(实用的)掩膜版过程中主要得一些方面。这些制造过程可分布图、布图编码和制版。这一节主要对那些正在作器件模拟的读者们有用处,他们可能需要设计一个包含若千个器件的供测试用的芯片。MOS晶体管版图。希望下面的资料将有助于使他们和制造工程师们(或硅产品制造厂)更容易相互配合。

MOS晶体管版图

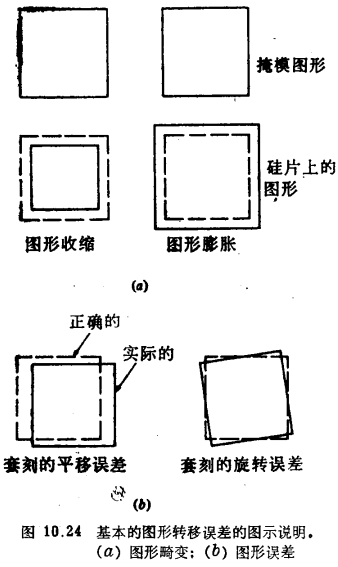

如10.1节所述,(布图)设计规则包含了一套对电路各层布图的几何约束,它与制造工艺中的空间分辨能力有关。当图形转移到硅片上时,后者受到图形畸变的限制,一些基本的畸变实例示于图10.24。一般,设计规则用长度的绝对单位来表示,例如微米。当各工序中的空间分辨能力改进后,设计规则便可按比例缩小,允许布图更密集些。在一般的生产设施中,总是不能按全套设计规则均匀的按比例缩小,因为在整个工艺过程中,工艺的空间分辨能力不是均匀的。MOS晶体管版图。然而,若允许用最差情况的分辨能力作为基本的工艺分辨能力,则就可能设计一套最简单的设计规则,随着工艺分辨能力不断改进,它可以均匀地按比例缩小。这样的规则广泛用于大学和对IC制造不熟悉的一些工业,并且可在电路设计的教科书中找到。

布图中的绘图可以用手工画,通常是用绘图工具。但是,现在几乎全部用那些可以买到的计算机辅助布图工具中的一种来完成。后者通常由计算机程序组成,通过视频计算机终端与设计者相互联系,并可在计算机终端上交互性的产生图形。这种工具有各种形式,从单独使用的到分时结构的都有。MOS晶体管版图。有一些是商业上可买到的,而其它很多都是在各种机构或大学中作为专用工具或研制的工具。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助