电子技术论坛

信息来源: 时间:2021-4-21

MOS晶体管在集成电路内结构举例及布线方法分析

本节举一个MOS集成电路的例子,叙述MOS晶体管在集成电路内是如何构成,如何连接的。

(1)MOS晶体管的概念

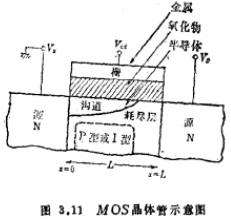

为便于理解,图3.11再画出MOS晶体管的剖面结构。在MOS结构的电容上加电压,就可以在半导体表面感生电荷,MOS晶体管就是利用感生电荷的电导性实现其工作的。在N沟道的场合,如在栅上加正电压,就会在半导体内感生电子,增加N区的源-漏之间的电流。MOS在集成电路内结构举例因此,集成电路结构由P型衬底内的两个N型区。这两个区域之间覆盖的绝缘膜、金属栅电极以及这些电极之间的连线构成。

(2)集成电路结构举例

图3.12给出N沟道MOS存储器大规模集成电路的局部放大照片及与之对应的排布图形。这一部分大致包括存储器触发器电路的一半。最下面看到一半的是放大晶体管,它上面是进行写入和读出的位晶体管,右上角为电源VDD。左侧为负载晶体管。

现以位于中心部分的位晶体管来说明晶体管的构成方法。

N型扩散区用单斜线表示,配置在上下两方。上侧的扩散区为该位晶体管专用;下侧的扩散区与放大晶体管的漏区共用。向左然后再向上延伸,与负载晶体管的源共用。

为了由上方的N型区引出电极,要除掉N型区中画交叉斜线部分的氧化膜,在此处覆盖铝电极,形成欧姆接触。

另外,栅电极与引线是共用的。与上下扩散区间隙部分重叠的铝电极横贯左右,同时构成栅区。

图3.12上部的负载晶体管与上述位晶体管的情形不同。此负载晶体管的栅和漏在电学上连在一起,均与电源电压相连,是一种名曰漏接地负载的形式。MOS在集成电路内结构举例。此处,栅电极与电源VDD相通,整个覆盖着铝电极。同时,为了增高这个负载晶体管的电阻值,减少其电流,应使栅宽度远小于栅长度,在源漏方向作成细长条的形状。

(3)布线方法

由图3.12也可以了解,MOS集成电路的交叉布线较双极型为易。双极型晶体管拓扑结构是,发射极被基极围住,基极又被集电极围住。因此,为了从发射极引出电极,如不通过覆盖绝缘层的基极和集电极部分从上面引出,在别处就引不出来。

但是,MOS晶体管中的源和漏是在不同的区域由同一扩散工序作成的。因此,在N沟道的场合,在P型衬底上各处都散在着N型区。对N沟道而言,电路内只存在正电位,这些处于P型衬底内的N型区为零偏置或反向偏置。因此,这种扩散区可作为引线使用。

今以图3.12的例子进行说明。位晶体管与放大晶体管共用的N型区可向左延伸然后向上延伸,与负载晶体管的源相连。此时位晶体管的栅电极也向左延伸并与扩散区交叉。MOS在集成电路内结构举例。这种交叉是扩散层与铝引线的交叉,二者之间用氧化膜隔离。容易实现这样的交叉布线是MOS晶体管的一个特点。因此,相当复杂的大规模集成电路也毋需靠多层布线实现。

MOS集成电路设计中值得注意的是设法不产生寄生的MOS器件。在3.2.4节中将要谈到,有一种方法可以避免产生寄生的MOS管,就是只在MOS晶体管的部分减薄绝缘膜,在其它布线处则增厚绝缘膜。图3.12中从位晶体管跨到放大晶体管用虚线表示的部分就是薄氧化膜的部分。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助