电子技术论坛

信息来源: 时间:2020-11-19

PMOS版图设计装置的制作方法

PMOS版图设计

版图设计是按照设计的要求和工艺条件,选择合适的尺寸,确定器件几何图形,进行合理的布局和连线,构成电路总版图,并按照工艺流程设计出一套光刻掩膜版。正确、良好的版图设计,不仅是实现电路功能所必需,而且对成品率、集成度以及电路性能都有很大的影响。PMOS版图设计

版图设计必须考虑三个原则:

①最有效地利用晶片面积;

②保证电路各方面的性能满足设计指标的要求;

③保证有较高的成品率。

为了达到这些目的,必须仔细研究各种布图方案,力求达到最佳。

目前中、小规模集成电路的版图设计往往凭借实践经验,靠人工完成,而大规模和超大规模集成电路的版图设计要采用计算机作辅助。这里就中、小规模集成电路版图设计的基本知识作些介绍。

1、版图基本尺寸的规定

在绘制版图时,作图的尺寸(包括四层掩膜图形尺寸)是必须认真考虑的。从提高集成度考虑,作图的尺寸当然愈小愈好,但要受到电学性能和工艺水平的限制。电学性能的限制,一般是指器件的漏源击穿特性、铝引线的最大电流密度以及引起寄生晶体管扩散条之间的最小间隙等等。工艺水平的限制主要指制版精度、前道工艺水平及光刻套准精度。PMOS版图设计。当然尺寸的规定不是一成不变的,而是随着工艺水平的提高而不断缩小的。例如,较早的PMOS常规工艺,沟道的最小长度一般设计为8~12μm,而目前先进的NMOS工艺,沟道长度L已缩小到2μm左右,甚至更小。

下面仅就PMOS常规工艺水平的图形尺寸的原则规定,分别作些介绍,以作入门参考。

(1)沟道最小尺寸的确定

上面讲到的MOS器件设计,给出了管子的宽长比。如何来确定沟道最小长度L,应从三个方面来考虑。

a、实际工艺水平。

b、源漏穿通电压。在第一章中讲到,L缩短,穿通电压 下降。为了保证源漏穿通电压大于MOS管的工作电压,要求

下降。为了保证源漏穿通电压大于MOS管的工作电压,要求 ,如果衬底浓度

,如果衬底浓度 ,则要求沟道最小宽度为:

,则要求沟道最小宽度为:

当然,电路的工作电压减小, 可以降低要求,L就可以减小。

可以降低要求,L就可以减小。

c、由于源漏区横向扩散的影响,会使实际的沟道长度要比版图上画出的小。一般横向扩散的长度取扩散结深 ,所以实际的沟道长度应为:

,所以实际的沟道长度应为:

如果结深为2μm,实际沟道长度 选为8μm,则绘制版图时,源漏间距应是12μm。

选为8μm,则绘制版图时,源漏间距应是12μm。

(2)一般图形尺寸

① 作图标记 为了使作图清楚,在同一图上分清扩散区、栅区、引线孔、铝引线条等四块光刻掩膜图形,一般各个区域都用不同的线条做标记。图5-3为1977年部颁发的MOS电路作图标记。

②尺寸规定 其它还有图形(或压点)与划片区的最小间隙为160~200μm;两块电路间距为520~600μm。

在图5-4中,其中 是后道工艺对电路尺寸的限制,如测试探针和热压焊点的大小,必须保证测试和压焊所需的面积;PMOS版图设计。又如用金刚刀划片,每个电路芯片之间必须保证有足够的间距;此外,压点与压点之间必须有一定的间隙,以保证压焊点相邻的金属丝不造成短路等等。

是后道工艺对电路尺寸的限制,如测试探针和热压焊点的大小,必须保证测试和压焊所需的面积;PMOS版图设计。又如用金刚刀划片,每个电路芯片之间必须保证有足够的间距;此外,压点与压点之间必须有一定的间隙,以保证压焊点相邻的金属丝不造成短路等等。

(3)扩散条间距的选定

MOS电路的扩散区主要是负载管的漏区(包括电源扩散区),倒相器两器件的公用扩散区,输入管的源区(包括接地扩散区)以及二个或三个晶体管的共用扩散区等等。在布图中,首先希望扩散区的布局能节省晶片面积,因此扩散区要均匀密集地分布在晶片上面,并充分利用共用扩散区。其次,扩散区的布局(包括器件的排布)要有利于铝引线的布局,使铝引线在版面上均匀分布,而不致疏密不均。第三,扩散区的布局还须避免寄生效应。如两扩散条间距很近,当铝线通过扩散区上面的厚氧化层时,会引起“场致反型晶体管”,如图5-5所示。这种寄生效应会引起严重的漏电或两扩散区穿通,增加电路的功耗和影响电路的性能。

场致反型晶体管的形成与两扩散区之间的距离有关。因为它的场致反型阀值电压 不仅与氧化层厚度有关,而且与两扩散区间距L有关(实际L就是寄生晶体管沟道长度)。下表给出了不同工值的

不仅与氧化层厚度有关,而且与两扩散区间距L有关(实际L就是寄生晶体管沟道长度)。下表给出了不同工值的 数值;

数值;

可见,在一些易于产生寄生效应的区域,两扩散区之间距离应适当加宽,最小间距为12μm。由于沟道的形成实际是渐近的过程,即使电压比 小得很多,也仍会有沟道漏电存在,所以设计中必须注意。PMOS版图设计。消除寄生效应,通常可采用以下两个办法:

小得很多,也仍会有沟道漏电存在,所以设计中必须注意。PMOS版图设计。消除寄生效应,通常可采用以下两个办法:

①铝线避开两扩散区的间隙;

②增大扩散条的间隙,如图5-6所示。

2、器件图形考虑

(1)一般器件图形

器件图形设计与扩散区的布局是分不开的。对于电路中倒相器的两个器件尺寸,布图时可有各种图形。一般来说,图形要简单,占用面积要小,所布图形要有利于发挥电路的性能。

对于共栅漏的负载器件, 值>1的情况,图形是很简单的,如图5-7(a)所示。

值>1的情况,图形是很简单的,如图5-7(a)所示。

对于 值<1的情况,根据电路具体布图可灵活设计,一般常用图形如图5-7(b)和(c)所示。

值<1的情况,根据电路具体布图可灵活设计,一般常用图形如图5-7(b)和(c)所示。

对于输入器件来说,较小尺寸很简单,较大尺寸的图形常见的有“L”形及“梳状”形,如图5-8所示。

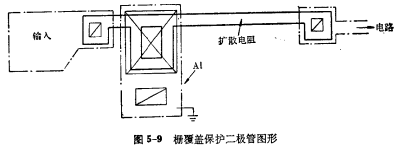

(2)栅保护器件图形

在整个电路的版图中,还包括栅保护器件,第一章中介绍了四种栅保护器件的形式。这里介绍两种经常采用的PMOS电路的栅保护器件图形。

图5-9所示为栅覆盖保护二极管图形。这种器件有一个相当长的边界,并且在二极管后面加了一个串联扩散电阻,以保证有较大的电流泄漏容量。

图5-10所示为栅调制保护二极管图形。

这两种器件,由于在PN结上制备了带有接地铝引线的薄氧化层,使二极管的反向击穿电压比一般二极管降低20~30V,所以实际击穿电压在40~60V的范围内。

3、铝引线布局原则

引线布局俗称“布线”,它是在决定了各器件于电路版中的位置后,用铝引线将各器件按电路的要求联结起来,这就是内部布线;PMOS版图设计。另外还有输入、输出、电源和接地压点的外部布线。

铝引线布局通常应注意以下几点:

①应尽可能道免寄生效应 高压线(输出点D)或电源线,一般应远离输入器件源、漏及栅极。

②连线电阻越小越好 可以适当加宽铝条,一般可用12~16μm。为了减小引线电阻的影响,电源线和地线尽可能采用铝线。但当无法采用铝线时,可采用扩散区作引线,但必引线孔须注意扩散电阻对电路性能的影响。

③铝引线应尽量避免使用长线 因为跨越的地方越多,产生针孔、断裂的机会也越多。当不可避免地一定要使用长引线时,铝线的条宽和厚度要适当增加。

④两线交叉时的隧道引线 隧道引线又称为原氧化层底下的扩散隐埋引线,这种扩散引线条与扩散源漏区同时做成,如图5-11所示。采用隧道引线,一般让低压(如接地线)经铝线引出,以免高压在薄氧化层上引起不良的泄漏影响。而高压线一般从扩散线引出。

4、绘制总图

根据给定的设计指标,计算出了电路中各器件的几何尺寸,再根据绘图的一些基本原则和规定,就可以着手设计和绘制电路的版子总图(即掩膜复合图),从而得到电路的光刻掩膜版。

(1)排版草图 一块性能优良的电路复合版,不是一次就能画好的。在正式画制版图以前,必须先绘制电路版子的草图。

其主要目的是:第一,大致安排一下各器件的位置;第二,画出内引线的连接图形,应避免内引线相互跨越;第三,确定输入和输出端引线的走向。在得到了一个满意的布局以后。再正式画制总图。

下面以某厂生产的4×3与非门PMOS电路(正逻辑规定)为例(如图5-12所示),作些简要的介绍。

对所有的电路来说,必须有输入、输出、电源、接地这些引出端。在这块电路中,共有4组与非门,每组有3个输入端,1个输出端,再加上公共的电源及接地端,所以总共有18个引出端。

各引出端的排列应符合标准化。PMOS版图设计。对于扁平陶瓷封装,它的管脚排列及编号如图5-13所示。这种P沟道系列电路,电源接第18脚,地线接第9脚,输入、输出端的排列如图中所示。这种4×3与非门电路,各组都是相同的,所以只要将一组中各管的位置编排好,按照对称原则,就可以将四组的图形编排在一块完整的版子里。

(2)绘制版子总图 版子总图(即掩膜复合图),根据制版工艺水平,一般采用放大200倍以上的作图比例,因为在这样的放大倍数情况下,最小尺寸的器件能够精确的画出来。根据排版草图,把电路的平面布图画在坐标纸上,即获得版子总图。PMOS版图设计。图5-14所示4×3与非门总图的四分之一。

总图完成后,必须仔细地检查和校对,特别是要注意以下几个问题

①器件尺寸是否正确,各种尺寸是否符合原则要求;

②连线是否正确,对照电路进行校对;

③是否有漏点、漏线现象,版子差错常常是忘了开引线孔或漏掉某些连线;

④是否有产生寄生MOS晶体管的地方;

⑤热压点排列是否符合封装要求。

在总图检查无误后,才可刻制分图(光刻掩膜版),提供制版使用。

联系方式:邹先生

联系电话:0755-83888366-8022

手机:18123972950

QQ:2880195519

联系地址:深圳市福田区车公庙天安数码城天吉大厦CD座5C1

请搜微信公众号:“KIA半导体”或扫一扫下图“关注”官方微信公众号

请“关注”官方微信公众号:提供 MOS管 技术帮助